May 17, 2013

W65C02S Datasheet

WDC reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. Information contained herein is provided gratuitously and without liability, to any user. Reasonable efforts have been made to verify the accuracy of the information but no guarantee whatsoever is given as to the accuracy or as to its applicability to particular uses. In every instance, it must be the responsibility of the user to determine the suitability of the products for each application. WDC products are not authorized for use as critical components in life support devices or systems. Nothing contained herein shall be construed as a recommendation to use any product in violation of existing patents or other rights of third parties. The sale of any WDC product is subject to all WDC Terms and Conditions of Sales and Sales Policies, copies of which are available upon request.

Copyright ©1981-2013 by The Western Design Center, Inc. All rights reserved, including the right of reproduction, in whole, or in part, in any form.

#### W65CO2S Datasheet

### **TABLE OF CONTENTS**

| 1 | IN7  | RODUCTION                                                      | 5       |

|---|------|----------------------------------------------------------------|---------|

|   | 1.1  | FEATURES OF THE W65C02S                                        | . 5     |

| 2 | FU   | NCTIONAL DESCRIPTION                                           | 6       |

|   | 2.1  | INSTRUCTION REGISTER (IR) AND DECODE                           |         |

|   | 2.1  | TIMING CONTROL UNIT (TCU)                                      | 0.<br>6 |

|   | 2.3  | ARITHMETIC AND LOGIC UNIT (ALU)                                | .6      |

|   | 2.4  | ACCUMULATOR REGISTER (A)                                       |         |

|   | 2.5  | INDEX REGISTERS (X AND Y)                                      |         |

|   | 2.6  | PROCESSOR STATUS REGISTER (P)                                  |         |

|   | 2.7  | PROGRAM COUNTER REGISTER (PC)                                  |         |

|   | 2.8  | STACK POINTER REGISTER (S)                                     |         |

| 3 | PΙΝ  | I FUNCTION DESCRIPTION                                         | 9       |

|   | 3.1  | Address Bus (A0-A15)                                           | . 9     |

|   | 3.2  | Bus Enable (BE)                                                |         |

|   | 3.3  | DATA BUS (D0-D7)                                               |         |

|   | 3.4  | INTERRUPT REQUEST (IRQB)                                       | . 9     |

|   | 3.5  | MEMORY LOCK (MLB)                                              |         |

|   | 3.6  | NON-MASKABLE INTERRUPT (NMIB)                                  | . 9     |

|   | 3.7  | No Connect (NC)                                                |         |

|   | 3.8  | Phase 2 In (PHI2), Phase 2 Out (PHI2O) and Phase 1 Out (PHI1O) |         |

|   | 3.9  | READ/WRITE (RWB)                                               |         |

|   | 3.10 | READY (RDY)                                                    |         |

|   | 3.11 | RESET (RESB)                                                   |         |

|   | 3.12 | SET OVERFLOW (SOB)                                             |         |

|   | 3.13 | SYNCHRONIZE WITH OPCODE FETCH (SYNC)                           |         |

|   | 3.14 | Power (VDD) and Ground (VSS)                                   |         |

|   | 3.15 | VECTOR PULL (VPB)                                              | 11      |

| 4 | AD   | DRESSING MODES1                                                | 15      |

|   | 4.1  | ABSOLUTE A                                                     | 15      |

|   | 4.2  | ABSOLUTE INDEXED INDIRECT (A,X)                                | 15      |

|   | 4.3  | ABSOLUTE INDEXED WITH X A,X                                    |         |

|   | 4.4  | ABSOLUTE INDEXED WITH Y A, Y                                   |         |

|   | 4.5  | ABSOLUTE INDIRECT (A)                                          |         |

|   | 4.6  | ACCUMULATOR A                                                  |         |

|   | 4.7  | IMMEDIATE ADDRESSING #                                         |         |

|   | 4.8  | IMPLIED I                                                      |         |

|   | 4.9  | PROGRAM COUNTER RELATIVE R                                     |         |

|   | 4.10 | STACK S                                                        |         |

|   | 4.11 | ZERO PAGE ZP                                                   |         |

|   |      | ZERO PAGE INDEXED INDIRECT (ZP,X)                              |         |

|   |      | ZERO PAGE INDEXED WITH X ZP,X                                  |         |

|   |      | ZERO PAGE INDEXED WITH Y ZP, Y                                 |         |

|   |      | ZERO PAGE INDIRECT (ZP)                                        |         |

|   | 4.16 | ZERO PAGE INDIRECT INDEXED WITH Y (ZP), Y                      | 19      |

| 5 | OP   | ERATION TABLES2                                                | 21      |

#### LU65CO2S Datasheet

| 6 DC, AC AND TIMING CHARACTERISTICS                                                                                                                       | 23 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.2 DC CHARACTERISTICS TA = -40°C to +85°C (PLCC, QFP) TA= 0°C to 70°C (DIP) 6.3 AC CHARACTERISTICS TA = -40°C to +85°C (PLCC, QFP) TA= 0°C to 70°C (DIP) |    |

| 7 CAVEATS                                                                                                                                                 |    |

| 8 HARD CORE MODEL                                                                                                                                         | 31 |

| 8.1 FEATURES OF THE W65C02S HARD CORE MODEL                                                                                                               | 31 |

| 9 SOFT CORE RTL MODEL                                                                                                                                     | 31 |

| 9.1 W65C02 SYNTHESIZABLE RTL-CODE IN VERILOG HDL                                                                                                          | 31 |

| 10 ORDERING INFORMATION                                                                                                                                   | 32 |

#### W65C02S Datasheet

### **TABLE OF TABLES**

| TABLE 3-1 VECTOR LOCATIONS                                        | 12 |

|-------------------------------------------------------------------|----|

| TABLE 3-2 PIN FUNCTION TABLE                                      | 12 |

| TABLE 4-1 ADDRESSING MODE TABLE                                   | 20 |

| TABLE 5-1 INSTRUCTION SET TABLE                                   |    |

| TABLE 5-2 W65C02S OPCODE MATRIX                                   | 22 |

| TABLE 6-1 ABSOLUTE MAXIMUM RATINGS                                | 23 |

| TABLE 6-2 DC CHARACTERISTICS                                      |    |

| TABLE 6-3 AC CHARACTERISTICS                                      | 25 |

| TABLE 6-4 OPERATION, OPERATION CODES AND STATUS REGISTER          |    |

| TABLE 7-1 MICROPROCESSOR OPERATIONAL ENHANCEMENTS                 | 30 |

|                                                                   |    |

| TABLE OF FIGURES                                                  |    |

|                                                                   |    |

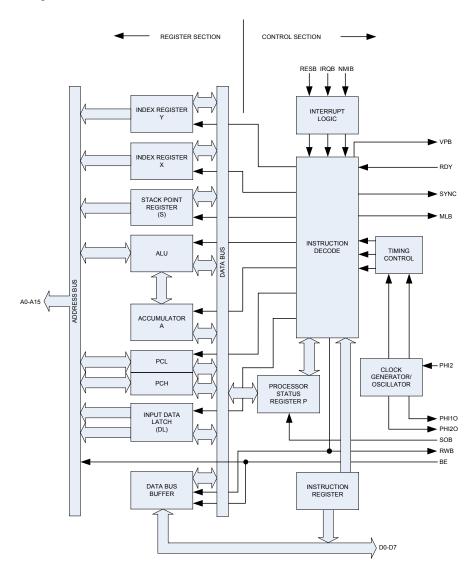

| FIGURE 2-1 W65C02S INTERNAL ARCHITECTURE SIMPLIFIED BLOCK DIAGRAM | 7  |

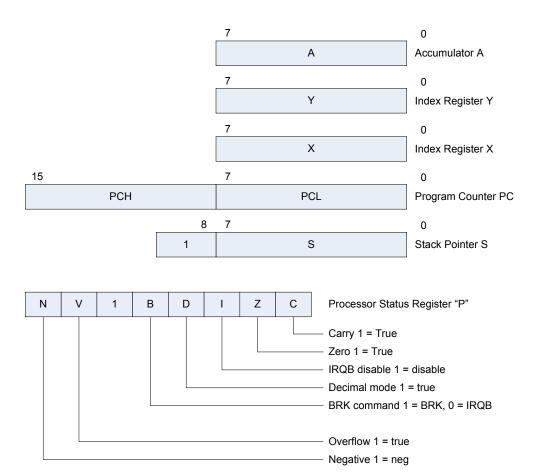

| FIGURE 2-2 W65C02S MICROPROCESSOR PROGRAMMING MODEL               | 8  |

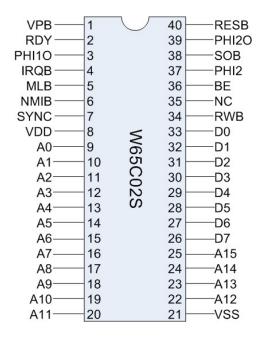

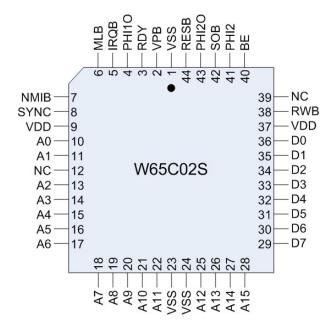

| FIGURE 3-1 W65C02S 40 PIN PDIP PINOUT                             | 13 |

| FIGURE 3-2 W65C02S 44 PIN PLCC PINOUT                             |    |

| FIGURE 3-3 W65C02S 44 PIN QFP PINOUT                              | 14 |

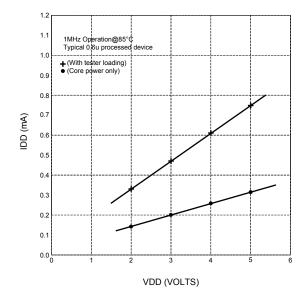

| FIGURE 6-1 IDD VS VDD                                             |    |

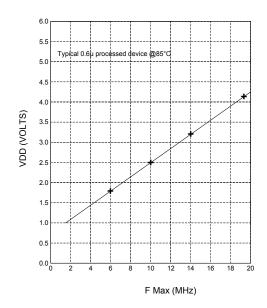

| FIGURE 6-2 F MAX VS VDD                                           |    |

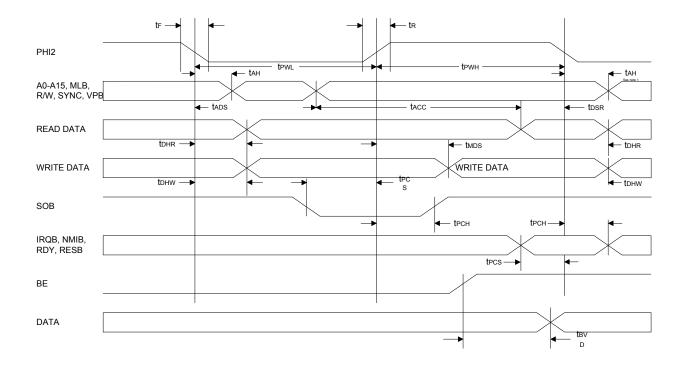

| FIGURE 6-3 GENERAL TIMING DIAGRAM                                 | 26 |

#### LU65CO2S Datasheet

#### 1 INTRODUCTION

The W65C02S is a low power cost sensitive 8-bit microprocessor. The W65C02S is a fully static core and the PHI2 clock can be stopped when it is in the high (logic 1) or low (logic 0) state. The variable length instruction set and manually optimized core size makes the W65C02S an excellent choice for low power System-on-Chip (SoC) designs. The Verilog RTL model is available for ASIC design flows. WDC, a Fabless Semiconductor Company, provides packaged chips for evaluation or volume production. To aid in system development, WDC provides a professional software development kit (ProSDK) for commercial development and an EduSDK for students and hobbyist projects.

You can find out more about our development hardware tools here:

http://www.westerndesigncenter.com/wdc/hardwaretools.cfm

And software tools here:

http://www.westerndesigncenter.com/wdc/tools.cfm

#### 1.1 Features of the W65C02S

- 8-bit data bus

- 16-bit address bus provides access to 65,536 bytes of memory space

- 8-bit ALU, Accumulator, Stack Pointer, Index Registers, Processor Status Register

- 16-bit Program Counter

- 69 instructions

- 16 addressing modes

- 212 Operation Codes (OpCodes)

- Vector Pull (VPB) output indicates when interrupt vectors are being addressed

- WAit-for-Interrupt (WAI) and SToP (STP) instructions reduce power consumption, decrease interrupt latency and provide synchronization with external events

- Variable length instruction set provides for lower power and smaller code optimization over fixed length instruction set processors

- Fully static circuitry

- Wide operating voltage range, 1.8+/- 5%, 2.5+/- 5%, 3.0+/- 5%, 3.3+/- 10%, 5.0+/- 5% specified

- Low Power consumption, 150uA@1MHz

#### W65C02S Datasheet

#### 2 FUNCTIONAL DESCRIPTION

The internal organization of the W65C02S is divided into two parts: 1) Register Section and 2) Control Section. Instructions obtained from program memory are executed by implementing a series of data transfers within the Register Section. Signals that cause data transfers are generated within the Control Section.

#### 2.1 Instruction Register (IR) and Decode

The Operation Code (OpCode) portion of the instruction is loaded into the Instruction Register from the Data Bus and is latched during the OpCode fetch cycle. The OpCode is then decoded, along with timing and interrupt signals, to generate various control signals for program execution.

#### 2.2 Timing Control Unit (TCU)

The Timing Control Unit (TCU) provides timing for each instruction cycle that is executed. The TCU is set to zero for each instruction fetch, and is advanced at the beginning of each cycle for as many cycles as is required to complete the instruction. Data transfers between registers depend upon decoding the contents of both the IR and the TCU.

#### 2.3 Arithmetic and Logic Unit (ALU)

All arithmetic and logic operations take place within the ALU. In addition to data operations, the ALU also calculates the effective address for relative and indexed addressing modes. The result of a data operation is stored in either memory or an internal register. Carry, Negative, Overflow and Zero flags are updated following the ALU data operation.

#### 2.4 Accumulator Register (A)

The Accumulator Register (A) is an 8-bit general purpose register which holds one of the operands and the result of arithmetic and logical operations. Reconfigured versions of this processor family could have additional accumulators.

#### 2.5 Index Registers (X and Y)

There are two 8-bit Index Registers (X and Y) which may be used as general purpose registers or to provide an index value for calculation of the effective address. When executing an instruction with indexed addressing, the microprocessor fetches the OpCode and the base address, and then modifies the address by adding the Index Register contents to the address prior to performing the desired operation.

#### 2.6 Processor Status Register (P)

The 8-bit Processor Status Register (P) contains status flags and mode select bits. The Carry (C), Negative (N), Overflow (V) and Zero (Z) status flags serve to report the status of ALU operations. These status flags are tested with Conditional Branch instructions. The Decimal (D) and IRQB disable (I) are used as mode select flags. These flags are set by the program to change microprocessor operations. Bit 5 is available for a user status or mode bit.

W65C02S Datasheet

#### 2.7 Program Counter Register (PC)

The 16-bit Program Counter Register (PC) provides the addresses which are used to step the microprocessor through sequential program instructions. This register is incremented each time an instruction or operand is fetched from program memory.

#### 2.8 Stack Pointer Register (S)

The Stack Pointer Register (S) is an 8-bit register which is used to indicate the next available location in the stack memory area. It serves as the effective address in stack addressing modes as well as subroutine and interrupt processing.

Figure 2-1 W65C02S Internal Architecture Simplified Block Diagram

#### LU65C02S Datasheet

Figure 2-2 W65C02S Microprocessor Programming Model

#### LU65CO2S Datasheet

#### 3 PIN FUNCTION DESCRIPTION

#### 3.1 Address Bus (A0-A15)

The sixteen bit Address Bus formed by A0-A15, address memory and I/O registers that exchange data on the Data Bus. The address lines can be set to the high impedance state by the Bus Enable (BE) signal.

#### 3.2 Bus Enable (BE)

The Bus Enable (BE) input signal provides external control of the Address, Data and the RWB buffers. When Bus Enable is high, the Address, Data and RWB buffers are active. When BE is low, these buffers are set to the high impedance status. Bus Enable is an asynchronous signal.

#### 3.3 Data Bus (D0-D7)

The eight Data Bus lines D0-D7 are used to provide instructions, data and addresses to the microprocessor and exchange data with memory and I/O registers. These lines may be set to the high impedance state by the Bus Enable (BE) signal.

#### 3.4 Interrupt Request (IRQB)

The Interrupt Request (IRQB) input signal is used to request that an interrupt sequence be initiated. The program counter (PC) and Processor Status Register (P) are pushed onto the stack and the IRQB disable (I) flag is set to a "1" disabling further interrupts before jumping to the interrupt handler. These values are used to return the processor to its original state prior to the IRQB interrupt. The IRQB low level should be held until the interrupt handler clears the interrupt request source. When Return from Interrupt (RTI) is executed the (I) flag is restored and a new interrupt can be handled. If the (I) flag is cleared in an interrupt handler, nested interrupts can occur. The Wait-for-Interrupt (WAI) instruction may be used to reduce power and synchronize with, as an example timer interrupt requests.

#### 3.5 Memory Lock (MLB)

The Memory Lock (MLB) output may be used to ensure the integrity of Read-Modify-Write instructions in a multiprocessor system. Memory Lock indicates the need to defer arbitration of the bus cycle when MLB is low. Memory Lock is low during the last three cycles of ASL, DEC, INC, LSR, ROL, ROR, TRB, and TSB memory referencing instructions.

#### 3.6 Non-Maskable Interrupt (NMIB)

A negative transition on the Non-Maskable Interrupt (NMIB) input initiates an interrupt sequence after the current instruction is completed. Since NMIB is an edge-sensitive input, an interrupt will occur if there is a negative transition while servicing a previous interrupt. Also, after the edge interrupt occurs no further interrupts will occur if NMIB remains low. The NMIB signal going low causes the Program Counter (PC) and Processor Status Register information to be pushed onto the stack before jumping to the interrupt handler. These values are used to return the processor to its original state prior to the NMIB interrupt.

#### 3.7 No Connect (NC)

The No Connect (NC) pins are not connected internally and should not be connected externally.

# WDC

### THE WESTERN DESIGN CENTER, INC.

LU65CO2S Datasheet

#### 3.8 Phase 2 In (PHI2), Phase 2 Out (PHI2O) and Phase 1 Out (PHI1O)

Phase 2 In (PHI2) is the system clock input to the microprocessor internal clock. During the low power Standby Mode, PHI2 can be held in either high or low state to preserve the contents of internal registers since the microprocessor is a fully static design. The Phase 2 Out (PHI2O) signal is generated from PHI2. Phase 1 Out (PHI1O) is the inverted PHI2 signal. An external oscillator is recommended for driving PHI2 and used for the main system clock. All production test timing is based on PHI2. PHI2O and PHI1O were used in older systems for system timing and internal oscillators when an external crystal was used.

#### 3.9 Read/Write (RWB)

The Read/Write (RWB) output signal is used to control data transfer. When in the high state, the microprocessor is reading data from memory or I/O. When in the low state, the Data Bus contains valid data to be written from the microprocessor and stored at the addressed memory or I/O location. The RWB signal is set to the high impedance state when Bus Enable (BE) is low.

#### 3.10 Ready (RDY)

A low input logic level on the Ready (RDY) will halt the microprocessor in its current state. Returning RDY to the high state allows the microprocessor to continue operation following the next PHI2 negative transition. This bi-directional signal allows the user to single-cycle the microprocessor on all cycles including write cycles. A negative transition to the low state prior to the falling edge of PHI2 will halt the microprocessor with the output address lines reflecting the current address being fetched. This assumes the processor setup time is met. This condition will remain through a subsequent PHI2 in which the ready signal is low. This feature allows microprocessor interfacing with low-speed memory as well as direct memory access (DMA). The WAI instruction pulls RDY low signaling the WAit-for-Interrupt condition, thus RDY is a bi-directional pin. On the W65C02 hard core there is a WAIT output signal that can be used in ASIC's thus removing the bi-directional signal and RDY becomes only the input. In such a situation the WAI instruction will pull WAIT low and must be used external of the core to pull RDY low or the processor will continue as if the WAI never happened. The microprocessor will be released when RDY is high and a falling edge of PHI2 occurs. This again assumes the processor control setup time is met. The RDY pin no longer has an active pull up. It is suggested that a pull up resistor be used on this pin when not being used. The RDY pin can still be wire ORed.

#### 3.11 Reset (RESB)

The Reset (RESB) input is used to initialize the microprocessor and start program execution. The RESB signal must be held low for at least two clock cycles after VDD reaches operating voltage. Ready (RDY) has no effect while RESB is being held low. All Registers are initialized by software except the Decimal and Interrupt disable mode select bits of the Processor Status Register (P) are initialized by hardware. When a positive edge is detected, there will be a reset sequence lasting seven clock cycles. The program counter is loaded with the reset vector from locations FFFC (low byte) and FFFD (high byte). This is the start location for program control. RESB should be held high after reset for normal operation.

Processor Status Register (P)

<sup>\*=</sup>software initialized

#### LU65CO2S Datasheet

#### 3.12 Set Overflow (SOB)

A negative transition on the Set Overflow (SOB) pin sets the overflow bit (V) in the status code register. The signal is sampled on the rising edge of PHI2. SOB was originally intended for fast input recognition because it can be tested with a branch instruction; however, it is not recommended in new system design and was seldom used in the past.

#### 3.13 SYNChronize with OpCode fetch (SYNC)

The OpCode fetch cycle of the microprocessor instruction is indicated with SYNC high. The SYNC output is provided to identify those cycles during which the microprocessor is fetching an OpCode. The SYNC line goes high during the clock cycle of an OpCode fetch and stays high for the entire cycle. If the RDY line is pulled low during the clock cycle in which SYNC went high, the processor will stop in its current state and will remain in the state until the RDY line goes high. In this manner, the SYNC signal can be used to control RDY to cause single instruction execution.

#### 3.14 Power (VDD) and Ground (VSS)

VDD is the positive power supply voltage and VSS is system logic ground.

#### 3.15 Vector Pull (VPB)

The Vector Pull (VPB) output indicates that a vector location is being addressed during an interrupt sequence. VPB is low during the last interrupt sequence cycles, during which time the processor reads the interrupt vector. The VPB signal may be used to select and prioritize interrupts from several sources by modifying the vector addresses.

#### W65C02S Datasheet

### **Table 3-1 Vector Locations**

| FFFE, F | BRK/IRQB | Software/Hardware |

|---------|----------|-------------------|

| FFFC, D | RESB     | Hardware          |

| FFFA, B | NMIB     | Hardware          |

**Table 3-2 Pin Function Table**

| Pin    | Description            |  |

|--------|------------------------|--|

| A0-A15 | Address Bus            |  |

| BE     | Bus Enable             |  |

| D0-D7  | Data Bus               |  |

| IRQB   | Interrupt Request      |  |

| MLB    | Memory Lock            |  |

| NC     | No Connection          |  |

| NMIB   | Non-Maskable Interrupt |  |

| PHI1O  | Phase 1 Out Clock      |  |

| PHI2   | Phase 2 In Clock       |  |

| PHI2O  | Phase 2 Out Clock      |  |

| RDY    | Ready                  |  |

| RESB   | Reset                  |  |

| RWB    | Read/Write             |  |

| SOB    | Set Overflow           |  |

| SYNC   | Synchronize            |  |

| VDD    | Positive Power Supply  |  |

| VPB    | Vector Pull            |  |

| VSS    | Internal Logic Ground  |  |

#### W65C02S Datasheet

Figure 3-1 W65C02S 40 Pin PDIP Pinout

Figure 3-2 W65C02S 44 Pin PLCC Pinout

W65C02S Datasheet

Figure 3-3 W65C02S 44 Pin QFP Pinout

W65C02S Datasheet

#### 4 ADDRESSING MODES

The W65C02S is capable of directly addressing 65,536 bytes of memory. The Program Address and Data Address space is contiguous throughout the 65,536 byte address space. Words, arrays, records, or any data structures may span the 65,536 byte address space. The following addressing mode descriptions provide additional detail as to how effective addresses are calculated. Sixteen addressing modes are available for the W65C02S. This address space has special significance within certain addressing modes.

#### 4.1 Absolute a

With Absolute addressing the second and third bytes of the instruction from the 16-bit address.

| Byte:            | 2   | 1   | 0      |

|------------------|-----|-----|--------|

| Instruction:     | ADH | ADL | OpCode |

|                  |     |     |        |

| Operand Address: |     | ADH | ADL    |

#### 4.2 Absolute Indexed Indirect (a,x)

With the Absolute Indexed Indirect addressing mode, the X Index Register is added to the second and third byes of the instruction to form an address to a pointer. This address mode is only used with the JMP instruction and the program Counter is loaded with the first and second bytes at this pointer.

| Byte:                  | 2   | 1         | 0       |

|------------------------|-----|-----------|---------|

| Instruction:           | ADH | ADL       | OpCode  |

|                        |     |           |         |

| Indirect Base address: |     | ADH       | ADL     |

|                        | +   |           | X       |

| Indirect address:      |     | effective | address |

| New PC value:          |     | indirect  | address |

#### 4.3 Absolute Indexed with X a,x

With the Absolute Indexed with X addressing mode, the X Index Register is added to the second and third bytes of the instruction to form the 16-bits of the effective address.

| Byte:            | 2   | 1         | 0       |

|------------------|-----|-----------|---------|

| Instruction:     | ADH | ADL       | OpCode  |

|                  |     |           |         |

|                  |     | ADH       | ADL     |

|                  | +   |           | Х       |

| Operand address: |     | effective | address |

#### LU65CO2S Datasheet

#### 4.4 Absolute Indexed with Y a, y

With the Absolute Indexed with Y addressing mode, the Y Index Register is added to the second and third bytes of the instruction to form the 16-bit effective address.

Byte:

2

1

0

Instruction:

ADH

ADL

OpCode

ADH

ADL

Y

Operand address:

effective address

#### 4.5 Absolute Indirect (a)

With the Absolute Indirect addressing mode, the second and third bytes of the instruction form an address to a pointer. This address mode is only used with the JMP instruction and the Program Counter is loaded with the first and second bytes at this pointer.

Byte:

2

1

0

Instruction:

ADH

ADL

OpCode

Indirect address:

ADH

ADL

New PC value:

indirect address

#### 4.6 Accumulator A

With Accumulator addressing the operand is implied as the Accumulator and therefore only a single byte forms the instruction.

Byte: 2 1 0

Instruction: OpCode

Operand: accumulator

#### 4.7 Immediate Addressing #

With Immediate Addressing the operand is the second byte of the instruction.

Byte: 2 1 0

Instruction: Operand OpCode

Operand: Operand

#### LU65C02S Datasheet

#### 4.8 Implied i

Implied addressing uses a single byte instruction. The operand is implicitly defined by the instruction.

Byte: 2 1 0

Instruction: OpCode

Operand address: implied

#### 4.9 Program Counter Relative r

The Program Counter relative addressing mode, sometimes referred to as Relative Addressing, is used with the Branch instructions. If the condition being tested is met, the second byte of the instruction is added to the Program Counter and program control is transferred to this new memory location.

Byte:

2

1

0

Instruction:

offset

OpCode

PCH

PCL

+

New PC value

effective address

#### 4.10 Stack s

The Stack may use memory from 0100 to 01FF and the effective address of the Stack address mode will always be within this range. Stack addressing refers to all instructions that push or pull data from the stack, such as Push, Pull, Jump to Subroutine, Return from Subroutine, Interrupts and Return from Interrupt.

Byte:

2

1

0

Instruction:

OpCode

Operand address:

1 | S

#### 4.11 Zero Page zp

With Zero Page (zp) addressing the second byte of the instruction is the address of the operand in page zero.

Byte:

2

1

0

Instruction:

zp

OpCode

Operand address:

0

zp

#### LU65C02S Datasheet

#### 4.12 Zero Page Indexed Indirect (zp,x)

The Zero Page Indexed Indirect addressing mode is often referred to as Indirect,X. The second byte of the instruction is the zero page address to which the X Index Register is added and the result points to the low byte of the indirect address.

| Byte:             | 2 | 1        | 0       |

|-------------------|---|----------|---------|

| Instruction:      |   | zp       | OpCode  |

|                   |   |          |         |

| Base Address:     |   |          | zp      |

|                   |   | +        | X       |

| Indirect Address: |   | 0        | address |

|                   |   |          |         |

| Operand address:  |   | indirect | address |

#### 4.13 Zero Page Indexed with X zp,x

With Zero Page Indexed with X addressing mode, the X Index Register is added to the second byte of instruction to form the effective address.

| Byte:            | 2 | 1  | 0                 |

|------------------|---|----|-------------------|

| Instruction:     |   | zp | OpCode            |

|                  |   |    |                   |

| Base Address:    |   |    | zp                |

|                  |   | +  | Χ                 |

| Operand Address: |   | 0  | effective address |

#### 4.14 Zero Page Indexed with Y zp, y

With Zero Page Indexed with Y addressing, the second byte of the instruction is the zero page address to which the Y Index Register is added to form the page zero effective address.

| Byte:            | 2 | 1  | 0                 |

|------------------|---|----|-------------------|

| Instruction:     |   | zp | OpCode            |

|                  |   |    |                   |

| Base Address:    |   |    | zp                |

|                  |   | +  | Υ                 |

| Operand Address: |   | 0  | effective address |

#### 4.15 Zero Page Indirect (zp)

With Zero Page Indirect addressing mode, the second byte of the instruction is a zero page indirect address that points to the low byte of a two byte effective address.

| Byte:             | 2 | 1                | 0      |

|-------------------|---|------------------|--------|

| Instruction:      |   | zp               | OpCode |

|                   |   |                  |        |

| Indirect Address: |   | 0                | zp     |

|                   |   |                  |        |

| Operand Address:  |   | indirect address |        |

#### W65C02S Datasheet

#### 4.16 Zero Page Indirect Indexed with Y (zp), y

The Zero Page Indirect Indexed with Y addressing mode is often referred to as Indirect Y. The second byte of the instruction points to the low byte of a two byte (16-bit) base address in page zero. Y Index Register is added to the base address to form the effective address.

| Byte:                  | 2 | 1           | 0           |

|------------------------|---|-------------|-------------|

| Instruction:           |   | zp          | OpCode      |

|                        |   |             |             |

| Indirect Base Address: |   | 0           | zp          |

|                        |   |             |             |

|                        |   | indirect ba | ase address |

|                        |   | +           | Υ           |

| Operand Address:       |   | effective   | e address   |

#### LU65C02S Datasheet

### **Table 4-1 Addressing Mode Table**

| Address Mode                                 | Instruction<br>Memory |         | •                     | on in Number of<br>quence Bytes |

|----------------------------------------------|-----------------------|---------|-----------------------|---------------------------------|

|                                              | Original<br>NMOS 6502 | W65C02S | Original<br>NMOS 6502 | W65C02S                         |

| 1. Absolute a                                | 4 (3)                 | 4 (3)   | 3                     | 3                               |

| 2. Absolute Indexed Indirect (a,x)           | 5                     | 5       | 3                     | 3                               |

| 3. Absolute Indexed with X a,x               | 4 (1,3)               | 4 (1,3) | 3                     | 3                               |

| 4. Absolute Indexed with Y a,y               | 4 (1)                 | 4 (1)   | 3                     | 3                               |

| 5. Absolute Indirect (a)                     | 4 (3)                 | 4 (3)   | 3                     | 3                               |

| 6. Accumulator A                             | 2                     | 2       | 1                     | 1                               |

| 7. Immediate #                               | 2                     | 2       | 2                     | 2                               |

| 8. Implied i                                 | 2                     | 2       | 1                     | 1                               |

| 9. Program Counter Relative r                | 2 (2)                 | 2 (2)   | 2                     | 2                               |

| 10. Stack s                                  | 3-7                   | 3-7     | 1-3                   | 1-4                             |

| 11. Zero Page zp                             | 3 (3)                 | 3 (3)   | 2                     | 2                               |

| 12. Zero Page Indexed Indirect (zp,x)        | 6                     | 6       | 2                     | 2                               |

| 13. Zero Page Indexed with X zp,x            | 4 (3)                 | 4 (3)   | 2                     | 2                               |

| 14. Zero Page Indexed with Y zp,y            | 4                     | 4       | 2                     | 2                               |

| 15. Zero Page Indirect (zp)                  | -                     | 5       | -                     | 2                               |

| 16. Zero Page Indirect Indexed with Y (zp),y | 5                     | 5       | 2                     | 2                               |

Notes: (indicated in parenthesis)

1. Page boundary, add 1 cycle if page boundary is crossed when forming address

2. Branch taken, add 1 cycle if branch is taken

3. Read-Modify-Write, add 2 cycles

#### W65CO2S Datasheet

### **5 OPERATION TABLES**

#### **Table 5-1 Instruction Set Table**

| 1.  | ADC  | ADd memory to accumulator with Carry                 |

|-----|------|------------------------------------------------------|

| 2.  | AND  | "AND" memory with accumulator                        |

| 3.  | ASL  | Arithmetic Shift one bit Left, memory or accumulator |

| 4.  | •BBR | Branch on Bit Reset                                  |

| 5.  | •BBS | Branch of Bit Set                                    |

| 6.  | BCC  | Branch on Carry Clear (Pc=0)                         |

| 7.  | BCS  | Branch on Carry Set (Pc=1)                           |

| 8.  | BEQ  | Branch if EQual (Pz=1)                               |

| 9.  | BIT  | Blt Test                                             |

| 10. | BMI  | Branch if result MInus (Pn=1)                        |

| 11. | BNE  | Branch if Not Equal (Pz=0)                           |

| 12. | BPL  | Branch if result PLus (Pn=0)                         |

| 13. | •BRA | BRanch Always                                        |

| 14. | BRK  | BReaK instruction                                    |

| 15. | BVC  | Branch on oVerflow Clear (Pv=0)                      |

| 16. | BVS  | Branch on oVerflow Set (Pv=1)                        |

| 17. | CLC  | CLear Cary flag                                      |

| 18. | CLD  | CLear Decimal mode                                   |

| 19. | CLI  | CLear Interrupt disable bit                          |

| 20. | CLV  | CLear oVerflow flag                                  |

| 21. | CMP  | CoMPare memory and accumulator                       |

| 22. | CPX  | ComPare memory and X register                        |

| 23. | CPY  | ComPare memory and Y register                        |

| 24. | DEC  | DECrement memory or accumulate by one                |

| 25. | DEX  | DEcrement X by one                                   |

| 26. | DEY  | DEcrement Y by one                                   |

| 27. | EOR  | "Exclusive OR" memory with accumulate                |

| 28. | INC  | INCrement memory or accumulate by one                |

| 29. | INX  | INcrement X register by one                          |

| 30. | INY  | INcrement Y register by one                          |

| 31. | JMP  | JuMP to new location                                 |

| 32. | JSR  | Jump to new location Saving Return (Jump to          |

|     |      | SubRoutine)                                          |

| 33. | LDA  | LoaD Accumulator with memory                         |

| 34. | LDX  | LoaD the X register with memory                      |

| 35. | LDY  | LoaD the Y register with memory                      |

| 36. | LSR  | Logical Shift one bit Right memory or                |

| 1 1 |      | accumulator                                          |

| 38. | ORA  | "OR" memory with Accumulator                             |

|-----|------|----------------------------------------------------------|

| 39. | PHA  | PusH Accumulator on stack                                |

| 40. | PHP  | PusH Processor status on stack                           |

| 41. | PHX  | PusH X register on stack                                 |

| 41. | PHY  | PusH Y register on stack                                 |

| 43. | PLA  | PuLI Accumulator from stack                              |

| 44. | PLP  | PuLI Processor status from stack                         |

| 45. | •PLX | PuLI X register from stack                               |

|     | •PLX |                                                          |

| 46. |      | PuLI Y register from stack                               |

| 47. | •RMB | Reset Memory Bit                                         |

| 48. | ROL  | ROtate one bit Left memory or accumulator                |

| 49. | ROR  | ROtate one bit Right memory or accumulator               |

| 50. | RTI  | ReTurn from Interrupt                                    |

| 51. | RTS  | ReTurn from Subroutine                                   |

| 52. | SBC  | SuBtract memory from accumulator with borrow (Carry bit) |

| 53. | SEC  | SEt Carry                                                |

| 54. | SED  | SEt Decimal mode                                         |

| 55. | SEI  | SEt Interrupt disable status                             |

| 56. | •SMB | Set Memory Bit                                           |

| 57. | STA  | STore Accumulator in memory                              |

| 58. | •STP | SToP mode                                                |

| 59. | STX  | STore the X register in memory                           |

| 60. | STY  | STore the Y register in memory                           |

| 61. | •STZ | STore Zero in memory                                     |

| 62. | TAX  | Transfer the Accumulator to the X register               |

| 63. | TAY  | Transfer the Accumulator to the Y register               |

| 64. | •TRB | Test and Reset memory Bit                                |

| 65. | •TSB | Test and Set memory Bit                                  |

| 66. | TSX  | Transfer the Stack pointer to the X register             |

| 67. | TXA  | Transfer the X register to the Accumulator               |

| 68. | TXS  | Transfer the X register to the Stack pointer register    |

| 69. | TYA  | Transfer Y register to the Accumulator                   |

| 70. | •WAI | WAit for Interrupt                                       |

Note:●= New Instruction

W65C02S Datasheet

### Table 5-2 W65C02S OpCode Matrix

| MSD |            |               |               |   |               |             | W65         | C02S Op      | Code N   | latrix     |            |            |                |            |              |             | MSD |

|-----|------------|---------------|---------------|---|---------------|-------------|-------------|--------------|----------|------------|------------|------------|----------------|------------|--------------|-------------|-----|

|     | 0          | 1             | 2             | 3 | 4             | 5           | 6           | 7            | 8        | 9          | А          | В          | С              | D          | E            | F           |     |

| 0   | BRK<br>a   | ORA<br>(zp,x) |               |   | TSB<br>zp •   | ORA<br>zp   | ASL<br>zp   | RMB0<br>zp • | PHP<br>s | ORA<br>#   | ASL<br>A   |            | TSB<br>a •     | ORA<br>a   | ASL<br>a     | BBR0<br>r•  | 0   |

| 1   | BPL<br>r   | ORA<br>(zp),y | ORA<br>(zp) * |   | TRB<br>zp •   | ORA<br>zp,x | ASL<br>zp,x | RMB1<br>zp • | CLC<br>i | ORA<br>a,y | INC<br>A * |            | TRB<br>a•      | ORA<br>a,x | ASL<br>a,x   | BBR1<br>r•  | 1   |

| 2   | JSR<br>a   | AND (zp,x)    |               |   | BIT<br>zp     | AND<br>zp   | ROL<br>zp   | RMB2<br>zp • | PLP<br>s | AND<br>#   | ROL<br>A   |            | BIT<br>a       | AND<br>a   | ROL<br>a     | BBR2<br>r • | 2   |

| 3   | BMI<br>r   | AND (zp),y    | AND (zp) *    |   | BIT<br>zp,x • | AND<br>zp,x | ROL<br>zp,x | RMB3<br>zp • | SEC<br>I | AND<br>a,y | DEC<br>A   |            | BIT<br>a,x *   | AND<br>a,x | ROL<br>a,x   | BBR3        | 3   |

| 4   | RTI<br>s   | EOR<br>(zp,x) |               |   |               | EOR<br>zp   | LSR<br>zp   | RMB4<br>zp • | PHA<br>s | EOR<br>#   | LSR<br>A * |            | JMP<br>a       | EOR<br>a   | LSR<br>a     | BBR4<br>r • | 4   |

| 5   | BVC<br>r   | EOR<br>(zp),y | EOR<br>(zp) * |   |               | EOR<br>zp,x | LSR<br>zp,x | RMB5<br>zp • | CLI<br>i | EOR<br>a,y | PHY<br>s•  |            |                | EOR<br>a,x | LSR<br>a,x   | BBR5<br>r • | 5   |

| 6   | RTS<br>s   | ADC (zp,x)    |               |   | STZ<br>zp •   | ADC<br>zp   | ROR<br>zp   | RMB6<br>zp • | PLA<br>s | ADC<br>#   | ROR<br>A   |            | JMP<br>(a)     | ADC<br>a   | ROR<br>a     | BBR6        | 6   |

| 7   | BVS<br>r   | ADC (zp),y    | ADC (zp) *    |   | STZ<br>zp,x • | ADC<br>zp,x | ROR<br>zp,x | RMB7<br>zp • | SEI<br>i | ADC<br>a,y | PLY<br>s•  |            | JMP<br>(a.x) * | ADC<br>a,x | ROR<br>a,x   | BBR7        | 7   |

| 8   | BRA<br>r • | STA<br>(zp,x) |               |   | STY<br>zp     | STA<br>zp   | STX<br>zp   | SMB0<br>zp • | DEY<br>i | BIT<br>#   | TXA<br>i   |            | STY<br>a•      | STA<br>a   | STX<br>a     | BBS0<br>r•  | 8   |

| 9   | BCC<br>r   | STA<br>(zp),y | STA (zp) *    |   | STY<br>zp,x   | STA<br>zp,x | STX<br>zp,y | SMB1<br>zp • | TYA<br>i | STA<br>a,y | TXS<br>i   |            | STZ<br>a       | STA<br>a,x | STZ<br>a,x • | BBS1        | 9   |

| А   | LDY<br>#   | LDA<br>(zp,x) | LDX<br>#*     |   | LDY<br>zp     | LDA<br>zp   | LDX<br>zp   | SMB2<br>zp • | TAY<br>i | LDA<br>#   | TAX<br>i   |            | LDY<br>a       | LDA<br>a   | LDX<br>a     | BBS2        | Α   |

| В   | BCS<br>r   | LDA<br>(zp),y | LDA<br>(zp) * |   | LDY<br>zp,x   | LDA<br>zp,x | LDX<br>zp,y | SMB3<br>zp • | CLV<br>i | LDA<br>A,y | TSX<br>i   |            | LDY<br>a,x     | LDA<br>a,x | LDX<br>a,x   | BBS3        | В   |

| С   | CPY<br>#   | CMP<br>(zp,x) |               |   | CPY<br>zp     | CMP<br>zp   | DEC<br>zp   | SMB4<br>zp • | INY<br>i | CMP<br>#   | DEX<br>i   | WAI<br>I • | CPY<br>a       | CMP<br>a   | DEC<br>a     | BBS4        | C   |

| D   | BNE<br>r   | CMP<br>(zp),y | CMP<br>(zp) * |   |               | CMP<br>zp,x | DEC<br>zp,x | SMB5<br>zp • | CLD<br>i | CMP<br>a,y | PHX<br>s • | STP<br>I•  |                | CMP<br>a,x | DEC<br>a,x   | BBS5        | D   |

| Е   | CPX<br>#   | SBC<br>(zp,x) |               |   | CPX<br>zp     | SBC<br>zp   | INC<br>zp   | SMB6<br>zp • | INX<br>i | SBC<br>#   | NOP<br>i   |            | CPX<br>a       | SBC<br>a   | INC<br>a     | BBS6        | Е   |

| F   | BEQ<br>r   | SBC<br>(zp),y | SBC<br>(zp) * |   |               | SBC<br>zp,x | INC<br>zp,x | SMB7<br>zp • | SED<br>i | SBC<br>a,y | PLX<br>s•  |            |                | SBC<br>a,x | INC<br>a,x   | BBS7        | F   |

|     | 0          | 1             | 2             | 3 | 4             | 5           | 6           | 7            | 8        | 9          | Α          | В          | С              | D          | Е            | F           |     |

<sup>\* =</sup> Old instruction with new addressing modes

<sup>● =</sup> New Instruction

W65C02S Datasheet

### 6 DC, AC AND TIMING CHARACTERISTICS

**Table 6-1 Absolute Maximum Ratings**

| Rating              | Symbol | Value             |

|---------------------|--------|-------------------|

| Supply Voltage      | VDD    | -0.3 to +7.0V     |

| Input Voltage       | VIN    | -0.3 to VDD +0.3V |

| Storage Temperature | TS     | -55°C to +150°C   |

This device contains input protection against damage due to high static voltages or electric fields; however, precautions should be taken to avoid application of voltages higher than the maximum rating.

Note: Exceeding these ratings may result in permanent damage. Functional operation under these conditions is not implied.

### 6.2 DC Characteristics TA = -40°C to +85°C (PLCC, QFP) TA= 0°C to 70°C (DIP)

#### **Table 6-2 DC Characteristics**

| Symbol     |                                                                                                                                                                   | 5.0 +/- 5          | %                  | 3.3 +/- 10         | 0%                         | 3.0 +/- 5          | %                  | 2.5 +/- 5          | %                  | 1.8 +/- 5%         |                    | Unit<br>s  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|----------------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|------------|

|            |                                                                                                                                                                   | Min                | Max                | Min                | Max                        | Min                | Max                | Min                | Max                | Min                | Max                |            |

| VDD        | Supply Voltage                                                                                                                                                    | 4.75               | 5.25               | 3.0                | 3.6                        | 2.85               | 3.15               | 2.37               | 2.63               | 1.71               | 1.89               | V          |

| Vih        | Input High Voltage (1)<br>BE, D0-D7, RDY, SOB<br>IRQB, NMIB, PHI2, RESB                                                                                           | VDDx0.7<br>VDD-0.4 | VDD+0.3<br>VDD+0.3 | VDDx0.7<br>VDD-0.4 | VDD+0.<br>3<br>VDD+0.<br>3 | VDDx0.7<br>VDD-0.4 | VDD+0.3<br>VDD+0.3 | VDDx0.7<br>VDD-0.4 | VDD+0.3<br>VDD+0.3 | VDDx0.7<br>VDD-0.4 | VDD+0.3<br>VDD+0.3 | V          |

| Vil        | Input Low Voltage (1)<br>BE, D0-D7, RDY, SOB,<br>IRQB, NMIB, PHI2, RESB                                                                                           | VSS-0.3<br>VSS-0.3 | VDDx0.3<br>VSS+0.4 | VSS-0.3<br>VSS-0.3 | VDDx0.<br>3<br>VSS+0.4     | VSS-0.3<br>VSS-0.3 | VDDx0.3<br>VSS+0.4 | VSS-0.3<br>VSS-0.3 | VDDx0.3<br>VSS+0.4 | VSS-0.3<br>VSS-0.3 | VDDx0.3<br>VSS+0.1 | V          |

| in         | Input Leakage Current (Vin=0.4 to 2.4, VDD=max) BE, IRQB, NMIB, PHI2, RESB, SOB, RDY                                                                              | -20                | 20                 | -20                | 20                         | -20                | 20                 | -20                | 20                 | -20                | 20                 | nA         |

| lin        | D0-D7 (off state)                                                                                                                                                 | -20                | 20                 | -20                | 20                         | -20                | 20                 | -20                | 20                 | -20                | 20                 | nA         |

| loh        | Output High current (Voh=VDD4, VDD=min)<br>A0-A15, D0-D7, MLB, PHI1O, PHI2O, RWB,<br>SYNC, VPB                                                                    | 700                | -                  | 350                | -                          | 300                | -                  | 200                | -                  | 100                | -                  | uA         |

| lol        | Output Low current (Vol=0.4, VDD=min)<br>A0-A15, D0-D7, MLB, PHI1O, PHI2O, RDY, RWB,<br>SYNC, VPB                                                                 | 1.6                | -                  | 1.6                | -                          | 1.6                | -                  | 1.0                | -                  | 0.5                | -                  | mA         |

| ldd        | Supply Current (with Tester Loading)<br>Supply Current (Core)                                                                                                     |                    | 1.5<br>0.5         | -                  | 1.0<br>0.3                 | -                  | 1.0<br>0.25        | -                  | 0.75<br>0.2        | -                  | 0.5<br>0.15        | mA/<br>MHz |

| Isby       | Standby Current Outputs Unloaded<br>BE, IRQB, NMIB, PHI2, SOB=VDD                                                                                                 | -                  | 1                  | -                  | 1                          | -                  | 1                  | -                  | 1                  | -                  | 1                  | uA         |

| Cin<br>Cts | *Capacitance (Vin=0V, TA=25°C, f-1MHz) BE, IRQB, NMIB, PHI2, RESB, RDY, SOB A0-A15, D0-D7, RWB *Not inspected during production test; verified on a sample basis. | -                  | 5                  | -                  | 5                          | -                  | 5                  | -                  | 5                  | -                  | 5                  | pF         |

(1) For high speed tests, Vih and Vil are set for VDD-.2v and VSS+.2V. The input "1" and "0" thresholds are tested at 1 MHz.

Figure 6-1 Idd vs Vdd

Figure 6-2 F Max vs Vdd

W65C02S Datasheet

#### 6.3 AC Characteristics TA = -40°C to +85°C (PLCC, QFP) TA= 0°C to 70°C (DIP)

#### **Table 6-3 AC Characteristics**

|        |                                 | 5.0 - | ·/-5% | 3.3 + | /-10% | 3.0 - | +/-5% | 2.5 +     | -/-5% | 1.8 -    | +/-5% |       |

|--------|---------------------------------|-------|-------|-------|-------|-------|-------|-----------|-------|----------|-------|-------|

| Symbol | Parameter                       | 141   | ИHz   | 8N    | lHz   | 18    | ИHz   | 4M        | Hz    |          | ИHz   | Units |

|        |                                 | Min   | Max   | Min   | Max   | Min   | Max   | Min       | Max   | Min      | Max   |       |

| VDD    | Supply Voltage                  | 4.75  | 5.25  | 3.0   | 3.6   | 2.85  | 3.15  | 2.37<br>5 | 2.675 | 1.7<br>1 | 1.89  | ٧     |

| tACC   | Access Time                     | 30    | -     | 70    | -     | 70    | -     | 145       | -     | 290      | -     | nS    |

| tAH    | Address Hold Time               | 10    | -     | 10    | -     | 10    | -     | 10        | -     | 10       | -     | nS    |

| tADS   | Address Setup Time              | -     | 30    | -     | 40    | -     | 40    | -         | 75    | -        | 150   | nS    |

| tBVD   | BE to Valid Data (1)            | -     | 25    | -     | 30    | -     | 30    | -         | 30    | -        | 30    | nS    |

| CEXT   | Capacitive Load (2)             | -     | 35    | -     | 35    | -     | 35    | -         | 35    | -        | 35    | pF    |

| tPWH   | Clock Pulse Width High          | 35    | -     | 62    | -     | 62    | -     | 125       | -     | 250      | -     | nS    |

| tPWL   | Clock Pulse Width Low           | 35    | -     | 63    | -     | 63    | -     | 125       | -     | 250      | -     | nS    |

| tCYC   | Cycle Time (3)                  | 70    | -     | 125   | -     | 125   | -     | 250       | -     | 500      | -     | nS    |

| tF,tR  | Fall Time, Rise Time            | -     | 5     | -     | 5     | -     | 5     | -         | 5     | -        | 5     | nS    |

| tPCH   | Processor Control Hold Time     | 10    | -     | 10    | -     | 10    | -     | 10        | -     | 10       | -     | nS    |

| tPCS   | Processor Control Setup<br>Time | 10    | 1     | 15    | -     | 15    | -     | 30        | -     | 60       | -     | nS    |

| tDHR   | Read Data Hold Time             | 10    | -     | 10    | -     | 10    | -     | 10        | -     | 10       | -     | nS    |

| tDSR   | Read Data Setup Time            | 10    | -     | 15    | -     | 15    | -     | 30        | -     | 60       | -     | nS    |

| tMDS   | Write Data Delay Time           | -     | 25    | -     | 40    | -     | 40    | -         | 70    | -        | 140   | nS    |

| tDHW   | Write Data Hold Time            | 10    | -     | 10    | -     | 10    | -     | 10        | -     | 10       | -     | nS    |

- 1. BE to High Impedance State is not testable but should be the same amount of time as BE to Valid Data

- 2. ATE or loading on all outputs

- 3. Since this is a static design, the maximum cycle time could be infinite.

W65C02S Datasheet

Figure 6-3 General Timing Diagram

#### Timing Notes:

- 1. Timing measurement points are 50% VDD.

- 2. PHI1O and PHI2O clock delay from PHI2 is no longer specified or tested and WDC recommends using an oscillator for system time base and PHI2 processor input clock.

W65C02S Datasheet

Table 6-4 Operation, Operation Codes and Status Register

|              | Table 6-4 C                                             | pci | auo   | , 🔾 | PCI | atic | ,,, C | Jour |    | III      | Ota | lus | 1,00   | gist | <u> </u> |      |        |                |                |              |                   |                  |             |     |           |

|--------------|---------------------------------------------------------|-----|-------|-----|-----|------|-------|------|----|----------|-----|-----|--------|------|----------|------|--------|----------------|----------------|--------------|-------------------|------------------|-------------|-----|-----------|

| nic          | Operation<br># Immediate Data<br>~ NOT<br>→ AND<br>v OR |     | (a,x) | a,× | a,y | (1   |       |      |    |          |     | d.  | (xb,x) | x'dz | zp,y     | (dz) | (zp),y |                | Prod           | cessor<br>*L | · Statu<br>Jser D | ıs Reg<br>efined | gister<br>d | (P) |           |

| Mnemomic     |                                                         | Ø   |       | Ø   | Ø   | (a)  | ⋖     | #    | -  | _        | S   | dz  | (Z)    | Z    | z        | ()   | Ŋ      | 7              | 6              | 5            | 4                 | 3                | 2           | 1   | 0         |

| Mne          |                                                         | 1   | 2     | 3   | 4   | 5    | 6     | 7    | 8  | 9        | 10  | 11  | 12     | 13   | 14       | 15   | 16     | N              | V              | 1            | 1                 | D                | ı           | Z   | С         |

| ADC          | A+M+C→A                                                 | 6D  |       | 7D  | 79  |      |       | 69   |    |          |     | 65  | 61     | 75   |          | 72   | 71     | N              | V              |              |                   |                  |             | Z   | С         |

| AND          | A^M→A                                                   | 2D  |       | 3D  | 39  |      |       | 29   |    |          |     | 25  | 21     | 35   |          | 32   | 31     | N              |                |              |                   | ٠                |             | Z   |           |

| ASL          | C←76543210←0                                            | 0E  |       | 1E  |     |      | 0A    |      |    |          |     | 06  |        | 16   |          |      |        | N              |                |              |                   |                  |             | Z   | С         |

| BBR0         | Branch on bit 0 reset                                   |     |       |     |     |      |       |      |    | 0F       |     |     |        |      |          |      |        | -              |                |              |                   | ٠                |             |     |           |

| BBR1         | Branch on bit 1 reset                                   |     |       |     |     |      |       |      |    | 1F       |     |     |        |      |          |      |        |                |                |              |                   | ٠                |             |     |           |

| BBR2         | Branch on bit 2 reset                                   |     |       |     |     |      |       |      |    | 2F       |     |     |        |      |          |      |        |                |                |              |                   | ٠                | •           | •   |           |

| BBR3         | Branch on bit 3 reset                                   |     |       |     |     |      |       |      |    | 3F       |     |     |        |      |          |      |        | -              | •              |              |                   |                  |             | •   | ٠         |

| BBR4         | Branch on bit 4 reset                                   |     |       |     |     |      |       |      |    | 4F       |     |     |        |      |          |      |        |                | •              | •            |                   | •                | •           | •   | ٠         |

| BBR5         | Branch on bit 5 reset                                   |     |       |     |     |      |       |      |    | 5F       |     |     |        |      |          |      |        | -              | •              | •            | •                 | •                | •           | •   |           |

| BBR6         | Branch on bit 6 reset                                   |     |       |     |     |      |       |      |    | 6F       |     |     |        |      |          |      |        |                | •              |              | ٠                 | ٠                | •           | •   | •         |

| BBR7         | Branch on bit 7 reset                                   |     |       |     |     |      |       |      |    | 7F       |     |     |        |      |          |      |        |                | •              |              | ٠                 | ٠                | •           | •   |           |

| BBS0         | Branch on bit 0 set                                     | -   |       | -   |     |      |       |      |    | 8F       |     |     |        |      |          |      |        |                | •              | •            |                   | •                | •           | •   |           |

| BBS1<br>BBS2 | Branch on bit 1 set                                     |     |       |     |     |      |       |      |    | 9F       |     |     |        |      |          |      |        |                | •              |              | ٠                 | ٠                | •           | •   | •         |

| BBS3         | Branch on bit 2 set                                     |     |       |     |     |      |       |      |    | AF<br>BF |     |     |        |      |          |      |        |                | •              | •            | ٠                 |                  | •           | •   | •         |

| BBS4         | Branch on bit 3 set                                     |     |       |     |     |      |       |      |    |          |     |     |        |      |          |      |        | •              | •              | •            | •                 |                  | •           | •   | -         |

| BBS5         | Branch on bit 4 set  Branch on bit 5 set                |     |       |     |     |      |       |      |    | CF<br>DF |     |     |        |      |          |      |        |                | •              | •            | ٠                 |                  | •           | •   | •         |

| BBS6         | Branch on bit 6 set                                     |     |       |     |     |      |       |      |    | EF       |     |     |        |      |          |      |        |                | •              | •            | •                 | •                | •           | •   | •         |

| BBS7         | Branch on bit 7 set                                     |     |       |     |     |      |       |      |    | FF       |     |     |        |      |          |      |        | •              | •              | •            | •                 | •                | •           | •   | -         |

| BCC          | Branch C = 0                                            |     |       |     |     |      |       |      |    | 90       |     |     |        |      |          |      |        |                | •              | •            | •                 | •                | •           | •   | •         |

| BCS          | Branch if C=1                                           |     |       |     |     |      |       |      |    | B0       |     |     |        |      |          |      |        |                | •              |              | ٠                 |                  | •           | •   | •         |

| BEQ          | Branch if Z=1                                           |     |       |     |     |      |       |      |    | F0       |     |     |        |      |          |      |        |                | •              | •            | •                 | -                | •           | •   | $\dot{-}$ |

| BIT          | A^M                                                     | 2C  |       | 3C  |     |      |       | 89   |    | '        |     | 24  |        | 34   |          |      |        | M <sub>7</sub> | M <sub>6</sub> | •            | •                 | •                | z           | •   |           |

| BMI          | Branch if N=0                                           | 20  |       |     |     |      |       |      |    | 30       |     |     |        | 01   |          |      |        | 1117           | 1416           | •            | •                 | •                | -           |     |           |

| BNE          | Branch if Z=0                                           |     |       |     |     |      |       |      |    | D0       |     |     |        |      |          |      |        |                |                |              |                   |                  |             |     | -         |

| BPL          | Branch if N=0                                           |     |       |     |     |      |       |      |    | 10       |     |     |        |      |          |      |        |                |                |              |                   |                  |             |     |           |

| BRA          | Branch Always                                           |     |       |     |     |      |       |      |    | 80       |     |     |        |      |          |      |        |                |                |              |                   |                  |             |     |           |

| BRK          | Break                                                   |     |       |     |     |      |       |      |    |          | 00  |     |        |      |          |      |        |                |                |              | 1                 | 0                | 1           |     | $\exists$ |

| вус          | Branch if V=0                                           |     |       |     |     |      |       |      |    | 50       |     |     |        |      |          |      |        |                |                |              |                   |                  |             |     |           |

| BVS          | Branch if V=1                                           |     |       |     |     |      |       |      |    | 70       |     |     |        |      |          |      |        |                |                |              |                   |                  |             |     |           |

| CLC          | C → 0                                                   |     |       |     |     |      |       |      | 18 |          |     |     |        |      |          |      |        |                |                |              |                   |                  |             |     | 0         |

| CLD          | 0 → D                                                   |     |       |     |     |      |       |      | D8 |          |     |     |        |      |          |      |        |                |                |              |                   | 0                |             |     |           |

| CLI          | 0 → 1                                                   |     |       |     |     |      |       |      | 58 |          |     |     |        |      |          |      |        |                |                |              |                   |                  | 0           |     |           |

| CLV          | 0 → V                                                   |     |       |     |     |      |       |      | В8 |          |     |     |        |      |          |      |        |                | 0              |              |                   |                  |             |     |           |

| СМР          | A-M                                                     | CD  |       | DD  | D9  |      |       | С9   |    |          |     | C5  | C1     | D5   |          | D2   | D1     | N              |                |              |                   |                  |             | Z   | С         |

| СРХ          | X-M                                                     | EC  |       |     |     |      |       | E0   |    |          |     | E4  |        |      |          |      |        | N              |                |              |                   |                  |             | Z   | С         |

| CPY          | Y-M                                                     | СС  |       |     |     |      |       | C0   |    |          |     | C4  |        |      |          |      |        | N              |                |              |                   |                  |             | Z   | С         |

| DEC          | Decrement                                               | CE  |       | DE  |     |      | ЗА    |      |    |          |     | C6  |        | D6   |          |      |        | N              |                |              |                   |                  |             | Z   |           |

| DEX          | $X-1 \rightarrow X$                                     | L   |       |     |     |      |       |      | CA |          |     |     |        |      |          |      |        | N              |                |              |                   |                  |             | Z   |           |

| DEY          | Y-1 → Y                                                 |     |       |     |     |      |       |      | 88 |          |     |     |        |      |          |      |        | N              |                |              |                   |                  |             | Z   |           |

| EOR          | $A \lor M \to A$                                        | 4D  |       | 5D  | 59  |      |       | 49   |    |          |     | 45  | 41     | 55   |          | 52   | 51     | N              |                |              |                   |                  |             | Z   |           |

| INC          | Increments                                              | EE  |       | FE  |     |      | 1A    |      |    |          |     | E6  |        | F6   |          |      |        | N              |                |              |                   |                  |             | Z   |           |

| INX          | X+1 → X                                                 |     |       |     |     |      |       |      | E8 |          |     |     |        |      |          |      |        | N              |                |              |                   |                  |             | Z   |           |

| INY          | $Y+1 \rightarrow Y$                                     |     |       |     |     |      |       |      | C8 |          |     |     |        |      |          |      |        | N              |                |              |                   |                  |             | Z   |           |

| JMP          | Jump to new location                                    | 4C  | 7C    |     |     | 6C   |       |      |    |          |     |     |        |      |          |      |        |                |                |              |                   |                  |             |     |           |

### W65C02S Datasheet

|          |                                                         |         | 1     |          | I            | I        | I             | 1      |         | I | 1       |         | I      | 1     |      | 1    | ı      | I      |        |   |                   |        |   |          |           |

|----------|---------------------------------------------------------|---------|-------|----------|--------------|----------|---------------|--------|---------|---|---------|---------|--------|-------|------|------|--------|--------|--------|---|-------------------|--------|---|----------|-----------|

| mic      | Operation<br># Immediate Data<br>~ NOT<br>^ AND<br>v OR |         | (×    |          |              |          |               |        |         |   |         |         | (zp,x) | ×     | γ,   | (0   | y,(qz) |        | Pro    |   | or Stat<br>User [ |        |   | (P)      |           |

| Mnemomic | xv Exclusive OR                                         | ro<br>1 | (a,×) | 3<br>x,a | У,<br>в<br>4 | (a)<br>5 | <b>∢</b><br>6 | #<br>7 | ·–<br>8 | 9 | σ<br>10 | 유<br>11 | 12     | x, dz | k'dz | (dz) | 16     | 7<br>N | 6<br>V | 5 | 4                 | 3<br>D | 2 | 1<br>Z   | 0<br>C    |

| JSR      | Jump to Subroutine                                      | 20      |       |          |              |          |               |        |         |   |         |         |        |       |      |      |        | N      |        |   |                   |        |   | Z        | <u> </u>  |

| LDA      | M → A                                                   | AD      |       | BD       | В9           |          |               | A9     |         |   |         | A5      | A1     | B5    |      | B2   | B1     | N      |        |   |                   |        |   | Z        |           |

| LDX      | $M \rightarrow X$                                       | AE      |       |          | BE           |          |               | A2     |         |   |         | A6      |        |       | В6   |      |        | N      |        |   |                   |        |   | Z        |           |

| LDY      | $M \rightarrow Y$                                       | AC      |       | ВС       |              |          |               | A0     |         |   |         | A4      |        | B4    |      |      |        | N      |        |   |                   |        |   | Z        |           |

| LSR      | $0 \rightarrow 76543210 \rightarrow C$                  | 4E      |       | 5E       |              |          | 4A            |        |         |   |         | 46      |        | 56    |      |      |        | 0      |        |   |                   |        |   | Z        | С         |

| NOP      | No Operation                                            |         |       |          |              |          |               |        | EA      |   |         |         |        |       |      |      |        |        |        |   |                   |        |   |          |           |

| ORA      | $A \lor M \rightarrow A$                                | 0D      |       | 1D       | 19           |          |               | 09     |         |   |         | 05      | 01     | 15    |      | 12   | 11     | N      |        |   |                   |        |   | Z        |           |

| PHA      | $A \rightarrow Ms, S-1 \rightarrow S$                   |         |       |          |              |          |               |        |         |   | 48      |         |        |       |      |      |        |        |        |   |                   |        |   |          |           |

| PHP      | $P \to Ms, S\text{-}1 \to S$                            |         |       |          |              |          |               |        |         |   | 08      |         |        |       |      |      |        |        |        |   |                   |        |   |          |           |

| PHX      | $X \rightarrow Ms, S-1 \rightarrow S$                   |         |       |          |              |          |               |        |         |   | DA      |         |        |       |      |      |        |        |        |   |                   |        |   | -        |           |

| PHY      | $Y \rightarrow Ms, S-1 \rightarrow S$                   |         |       |          |              |          |               |        |         |   | 5A      |         |        |       |      |      |        |        |        |   |                   |        |   |          |           |

| PLA      | $S + 1 \rightarrow S$ , $Ms \rightarrow A$              |         |       |          |              |          |               |        |         |   | 68      |         |        |       |      |      |        | N      |        |   |                   |        |   | Z        |           |

| PLP      | $S + 1 \rightarrow S$ , $Ms \rightarrow P$              |         |       |          |              |          |               |        |         |   | 28      |         |        |       |      |      |        | N      | V      |   | 1                 | D      | ı | Z        | С         |

| PLX      | $S + 1 \rightarrow S$ , $Ms \rightarrow X$              |         |       |          |              |          |               |        |         |   | FA      |         |        |       |      |      |        | N      |        |   |                   |        |   | Z        |           |

| PLY      | $S + 1 \rightarrow S$ , $Ms \rightarrow Y$              |         |       |          |              |          |               |        |         |   | 7A      |         |        |       |      |      |        | N      |        |   |                   |        |   | Z        |           |

| RMB0     | Reset Memory Bit 0                                      |         |       |          |              |          |               |        |         |   |         | 07      |        |       |      |      |        |        |        |   |                   |        |   |          |           |

| RMB1     | Reset Memory Bit 1                                      |         |       |          |              |          |               |        |         |   |         | 17      |        |       |      |      |        |        |        |   |                   |        |   |          |           |

| RMB2     | Reset Memory Bit 2                                      |         |       |          |              |          |               |        |         |   |         | 27      |        |       |      |      |        |        |        |   |                   |        |   |          |           |

| RMB3     | Reset Memory Bit 3                                      |         |       |          |              |          |               |        |         |   |         | 37      |        |       |      |      |        |        |        |   |                   |        |   |          | $\dashv$  |

| RMB4     | Reset Memory Bit 4                                      |         |       |          |              |          |               |        |         |   |         | 47      |        |       |      |      |        |        |        |   |                   |        |   |          |           |

| RMB5     | Reset Memory Bit 5                                      |         |       |          |              |          |               |        |         |   |         | 57      |        |       |      |      |        |        | -      |   |                   |        |   |          |           |